1200V HIGH VOLTAGE HALF BRIDGE DRIVER

#### **DESCRIPTION**

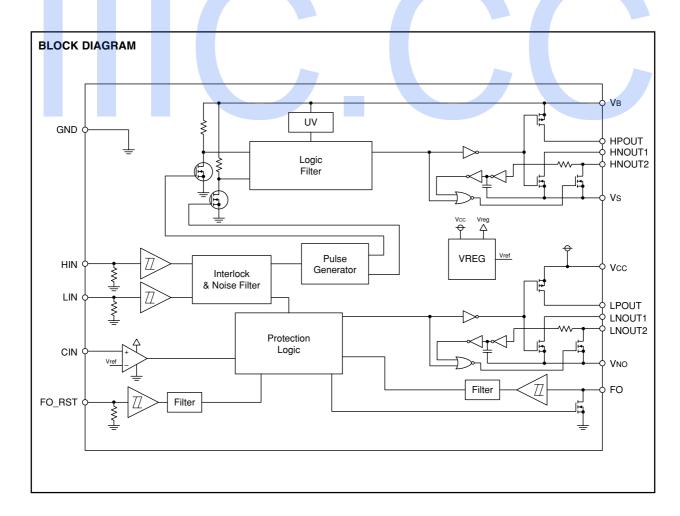

M81019FP is high voltage Power MOSFET and IGBT gate driver for half bridge applications.

#### **FEATURES**

- Floating supply voltage up to 1200V

- Low quiescent power supply current

- Separate sink and source current output up to ±1A (typ)

- Active Miller effect clamp NMOS with sink current up to −1 A (typ)

- Input noise filters

- Over-current detection and output shutdown

- High side under voltage lockout

- FO pin which can input and output Fault signals to communicate with controllers and synchronize the shut down with other phases

- Pb-free

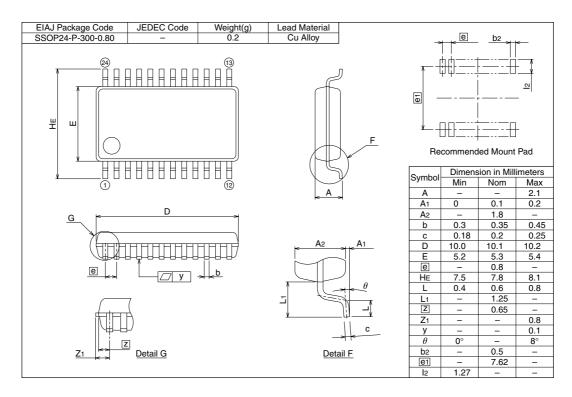

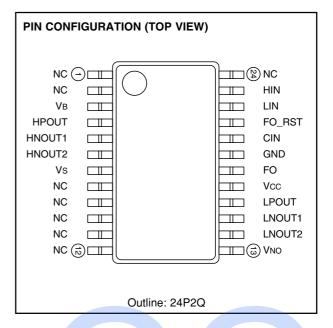

- 24-Lead SSOP package

#### **APPLICATIONS**

Power MOSFET and IGBT gate driver for Medium and Micro inverter or general purpose.

#### **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings indicate limitation beyond which destruction of device may occur. All voltage parameters are absolute voltage reference to GND unless otherwise specified.

| Symbol   | Parameter                                  | Test conditions   | Ratings             | Unit  |

|----------|--------------------------------------------|-------------------|---------------------|-------|

| Vв       | High side floating supply absolute voltage |                   | <b>−</b> 0.5 ~ 1224 | V     |

| Vs       | High side floating supply offset voltage   |                   | VB-24 ~ VB+0.5      | V     |

| VBS      | High side floating supply voltage          | VBS = VB-VS       | <b>−</b> 0.5 ~ 24   | V     |

| Vно      | High side output voltage                   |                   | Vs-0.5 ~ VB+0.5     | V     |

| Vcc      | Low side fixed supply voltage              |                   | <b>−</b> 0.5 ~ 24   | V     |

| Vno      | Power ground                               |                   | Vcc-24 ~ Vcc+0.5    | V     |

| VLO      | Low side output voltage                    |                   | VNO-0.5 ~ VCC+0.5   | V     |

| VIN      | Logic input voltage                        | HIN, LIN, FO_RST  | -0.5 ~ Vcc+0.5      | V     |

| VFO      | FO input/output voltage                    |                   | -0.5 ~ Vcc+0.5      | V     |

| VCIN     | CIN input voltage                          |                   | -0.5 ~ Vcc+0.5      | V     |

| dVs/dt   | Allowable offset voltage slew rate         |                   | ±50                 | V/ns  |

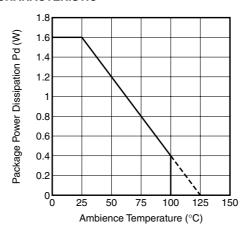

| Pd       | Package power dissipation                  | Ta = 25°C, On PCB | 1.6                 | W     |

| Kθ       | Linear derating factor                     | Ta > 25°C, On PCB | 16                  | mW/°C |

| Rth(j-c) | Junction-case thermal resistance           |                   | 60                  | °C/W  |

| Tj       | Junction temperature                       |                   | -40 ~ 125           | °C    |

| Topr     | Operation temperature                      |                   | <b>−40 ~ 100</b>    | °C    |

| Tstg     | Storage temperature                        |                   | <b>−40 ~ 125</b>    | °C    |

#### RECOMMENDED OPERATING CONDITIONS

For proper operation the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to GND unless otherwise specified.

| 0 1 1  | Б                                          | T . 100          |            | Limits |       |      |  |

|--------|--------------------------------------------|------------------|------------|--------|-------|------|--|

| Symbol | Parameter                                  | Test conditions  | Min.       | Тур.   | Max.  | Unit |  |

| VB     | High side floating supply absolute voltage |                  | Vs+13.5    | Vs+15  | Vs+20 | V    |  |

| Vs     | High side floating supply offset voltage   | VBS > 13.5V      | <b>-</b> 5 | _      | 900   | V    |  |

| VBS    | High side floating supply voltage          | VBS = VB-VS      | 13.5       | 15     | 20    | V    |  |

| VHO    | High side output voltage                   |                  | Vs         | _      | Vs+20 | V    |  |

| Vcc    | Low side fixed supply voltage              |                  | 13.5       | _      | 20    | V    |  |

| Vno    | Power ground                               |                  | -0.5       | _      | 5     | V    |  |

| VLO    | Low side output voltage                    |                  | VNO        | _      | Vcc   | V    |  |

| VIN    | Logic input voltage                        | HIN, LIN, FO_RST | 0          | 5      | Vcc   | V    |  |

| VFO    | FO input/output voltage                    |                  | 0          | _      | Vcc   | V    |  |

| VCIN   | CIN input voltage                          |                  | 0          | _      | 5     | V    |  |

Note : For proper operation, the device should be used within the recommend conditions.

### THERMAL DERATING FACTOR CHARACTERISTIC

# 1200V HIGH VOLTAGE HALF BRIDGE DRIVER

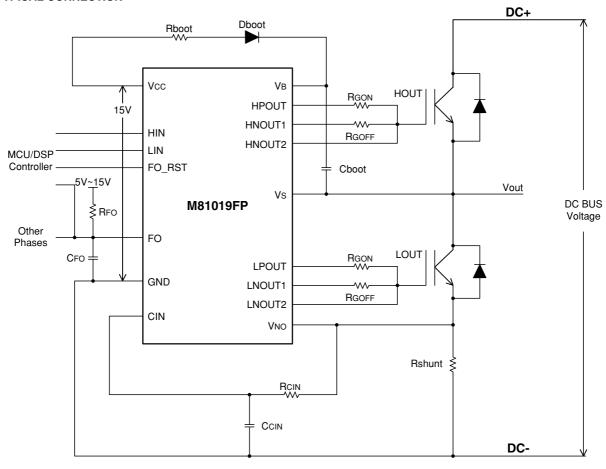

# **TYPICAL CONNECTION**

Note: If HVIC is working in high noise environment, it is recommended to connect a 1nF ceramic capacitor (CFO) to FO pin.

# 1200V HIGH VOLTAGE HALF BRIDGE DRIVER

# ELECTRICAL CHARACTERISTICS (Ta=25°C, Vcc=VBS (=VB-VS)=15V, unless otherwise specified)

| Symbol   Parameter   Test conditions   Min.   Typ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Max. 1.0 0.8 1.5 0.5 0.6 1.4 0.01 500                    | Unit μA mA V V V V mA mA ns        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|

| IBS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.8<br>1.5<br>—<br>0.5<br>—<br>0.6<br>1.4<br>0.01<br>500 | mA mA V V V V mA mA                |

| ICC         Vcc quiescent supply current         HIN = LIN = 0V         —         1           VOH         High level output voltage         IO = -20mA, HPOUT, LPOUT         14.5         —           VOL         Low level output voltage         IO = 20mA, HNOUT1, LNOUT1         —         —           VIH         High level input threshold voltage         HIN, LIN, FO_RST         4.0         —           VIL         Low level input threshold voltage         HIN, LIN, FO_RST         —         —           IIH         High level input bias current         VIN = 5V         0.6         1           IIL         Low level input bias current         VIN = 0V         —0.01         0           tFilter         Input signals filter time         HIN, LIN, FO_RST, FO         80         200           VHNO2         High side active Miller clamp NMOS input threshold voltage         VIN = 0V         2.0         3.4 | 1.5<br>— 0.5<br>— 0.6<br>1.4<br>0.01<br>500              | mA<br>V<br>V<br>V<br>V<br>mA<br>mA |

| VOH         High level output voltage         Io = -20mA, HPOUT, LPOUT         14.5         —           VOL         Low level output voltage         Io = 20mA, HNOUT1, LNOUT1         —         —           VIH         High level input threshold voltage         HIN, LIN, FO_RST         4.0         —           VIL         Low level input threshold voltage         HIN, LIN, FO_RST         —         —           IIH         High level input bias current         VIN = 5V         0.6         1           IIL         Low level input bias current         VIN = 0V         —0.01         0           tFilter         Input signals filter time         HIN, LIN, FO_RST, FO         80         200           VHNO2         High side active Miller clamp NMOS input threshold voltage         VIN = 0V         2.0         3.4                                                                                               | 0.5<br><br>0.6<br>1.4<br>0.01<br>500                     | V V V V mA mA                      |

| VOL         Low level output voltage         Io = 20mA, HNOUT1, LNOUT1         —         —           VIH         High level input threshold voltage         HIN, LIN, FO_RST         4.0         —           VIL         Low level input threshold voltage         HIN, LIN, FO_RST         —         —           IIH         High level input bias current         VIN = 5V         0.6         1           IIL         Low level input bias current         VIN = 0V         —0.01         0           tFilter         Input signals filter time         HIN, LIN, FO_RST, FO         80         200           VHNO2         High side active Miller clamp NMOS input threshold voltage         VIN = 0V         2.0         3.4                                                                                                                                                                                                       | 0.5<br>— 0.6<br>1.4<br>0.01<br>500                       | V<br>V<br>V<br>mA<br>mA            |

| VIH         High level input threshold voltage         HIN, LIN, FO_RST         4.0         —           VIL         Low level input threshold voltage         HIN, LIN, FO_RST         —         —           IIH         High level input bias current         VIN = 5V         0.6         1           IIL         Low level input bias current         VIN = 0V         —0.01         0           tFilter         Input signals filter time         HIN, LIN, FO_RST, FO         80         200           VHNO2         High side active Miller clamp NMOS input threshold voltage         VIN = 0V         2.0         3.4                                                                                                                                                                                                                                                                                                            | 0.6<br>1.4<br>0.01<br>500                                | V<br>V<br>mA<br>mA                 |

| VIL         Low level input threshold voltage         HIN, LIN, FO_RST         —         —           IIH         High level input bias current         VIN = 5V         0.6         1           IIL         Low level input bias current         VIN = 0V         —0.01         0           tFilter         Input signals filter time         HIN, LIN, FO_RST, FO         80         200           VHNO2         High side active Miller clamp NMOS input threshold voltage         VIN = 0V         2.0         3.4                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.4<br>0.01<br>500                                       | V<br>mA<br>mA                      |

| IIH         High level input bias current         VIN = 5V         0.6         1           IIL         Low level input bias current         VIN = 0V         -0.01         0           tFilter         Input signals filter time         HIN, LIN, FO_RST, FO         80         200           VHNO2         High side active Miller clamp NMOS input threshold voltage         VIN = 0V         2.0         3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.4<br>0.01<br>500                                       | mA<br>mA                           |

| IIIL         Low level input bias current         VIN = 0V         -0.01         0           tFilter         Input signals filter time         HIN, LIN, FO_RST, FO         80         200           VHNO2         High side active Miller clamp NMOS input threshold voltage         VIN = 0V         2.0         3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.01<br>500                                              | mA                                 |

| tFilter Input signals filter time HIN, LIN, FO_RST, FO 80 200  VHNO2 High side active Miller clamp NMOS input threshold voltage VIN = 0V 2.0 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 500                                                      |                                    |

| VHNO2 High side active Miller clamp NMOS input threshold voltage VIN = 0V 2.0 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          | ns                                 |

| VHNO2 VIN = 0V 2.0 3.4 input threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                        | 1                                  |

| input threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                        | V                                  |

| 1 11 11 11 11 11 11 11 11 11 11 11 11 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          | \ \ \                              |

| $V_{LNO2}$ Low side active Miller clamp NMOS $V_{IN} = 0V$ 6.0 7.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                                                        | V                                  |

| input threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          | "                                  |

| tVNO2 Active Miller clamp NMOS filter time VIN = 0V — 400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          | ns                                 |

| VOLFO Low level FO output voltage IFO = 1mA — 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.95                                                     | V                                  |

| VIHFO High level FO input threshold voltage 4.0 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                        | V                                  |

| VILFO Low level FO input threshold voltage — — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.6                                                      | V                                  |

| VBSuvr VBS supply UV reset voltage 10.5 11.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12.1                                                     | V                                  |

| VBSuvt VBS supply UV trip voltage 10 10.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11.6                                                     | V                                  |

| VBSuvh VBS supply UV hysteresis voltage VBSuvh = VBSuvr–VBSuvt 0.2 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.8                                                      | V                                  |

| tVBsuv VBs supply UV filter time 4 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16                                                       | μs                                 |

| VCIN CIN trip voltage 0.4 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.6                                                      | V                                  |

| VPOR POR trip voltage 4 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.5                                                      | V                                  |

| IOH Output high level short circuit pulsed current HPOUT (LPOUT) = 0V, HIN = 5V, PW < 5μs — 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          | Α                                  |

| IOL1 Output low level short circuit pulsed current HNOUT1 (LNOUT1) = 15V, LIN = 5V, PW < 5μs — —1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                        | Α                                  |

| loL2 Active Miller clamp NMOS output HNOUT2 (LNOUT2) = 15V, LIN = 5V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                        | Α                                  |

| low level short circuit pulsed current PW < 5μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          | Α                                  |

| ROH Output high level on resistance IO = -1A, ROH = (VOH-VO) /IO — 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                        | Ω                                  |

| RoL1 Output low level on resistance Io = 1A, RoL1 = Vo/Io — 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          | Ω                                  |

| RoL2 Active Miller clamp NMOS output Io = 1A, RoL2 = Vo/Io — 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          | Ω                                  |

| low level on resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          | 22                                 |

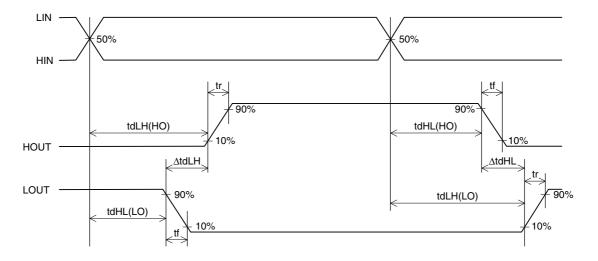

| tdLH(HO) High side turn-on propagation delay HPOUT short to HNOUT1 and HNOUT2, CL = 1nF 1 1.27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.8                                                      | μs                                 |

| tdHL(HO) High side turn-off propagation delay HPOUT short to HNOUT1 and HNOUT2, CL = 1nF 0.9 1.21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.8                                                      | μs                                 |

| tdLH(LO) Low side turn-on propagation delay LPOUT short to LNOUT1 and LNOUT2, CL = 1nF 1 1.39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.9                                                      | μs                                 |

| tdHL(LO) Low side turn-off propagation delay LPOUT short to LNOUT1 and LNOUT2, CL = 1nF 0.9 1.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.7                                                      | μs                                 |

| tr Output turn-on rise time CL = 1nF — 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T -                                                      | ns                                 |

| tf Output turn-off fall time CL = 1nF — 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                                                        | ns                                 |

| ΔtdLH Delay matching, high side turn-on tdLH (HO)-tdHL (LO) — 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | ns                                 |

| and low side turn-off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          | 115                                |

| ΔtdHL Delay matching, high side turn-off tdLH (LO)-tdHL (HO) — 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          | ns                                 |

| and low side turn-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          | 115                                |

Note: Typ is not specified.

# 1200V HIGH VOLTAGE HALF BRIDGE DRIVER

# FUNCTION TABLE (Q: Keep previous status)

| HIN | LIN | FO_RST | CIN | FO<br>(Input) | VBS/UV | Vcc/POR | HOUT | LOUT | FO<br>(Output) | Behavioral status                      |

|-----|-----|--------|-----|---------------|--------|---------|------|------|----------------|----------------------------------------|

| H→L | L   | L      | L   | -             | Н      | Н       | L    | L    | Н              |                                        |

| H→L | Н   | L      | L   | -             | Н      | Н       | L    | Н    | Н              |                                        |

| L→H | L   | L      | L   | -             | Н      | Н       | Н    | L    | Н              |                                        |

| L→H | Н   | L      | L   | -             | Н      | Н       | Q    | Q    | Н              | Interlock active                       |

| Х   | Н   | Х      | Η   | ı             | Х      | Н       | L    | L    | L              | CIN tripping when LIN=H                |

| Х   | L   | Х      | Η   | 1             | Х      | Н       | Q    | Q    | Н              | CIN not tripping when LIN=L            |

| Х   | Х   | Х      | Х   | L             | Х      | Н       | L    | L    | L              | Output shuts down when FO=L            |

| Х   | Х   | Х      | Х   | -             | Х      | L       | L    | L    | Н              | Vcc power reset                        |

| Х   | L   | L      | L   | _             | L      | Н       | L    | L    | Н              | VBS power reset                        |

| Х   | Н   | L      | L   | -             | Ĺ      | Н       | L    | Н    | Н              | VBS power reset is tripping when LIN=H |

Note1: "L" status of VBS/UV indicates a high side UV condition; "L" status of Vcc/POR indicates a Vcc power reset condition.

- 2 : In the case of both input signals (HIN and LIN) are "H", output signals (HOUT and LOUT) keep previous status.

- $3: X (HIN): L \rightarrow H \text{ or } H \rightarrow L. \text{ Other } : H \text{ or } L.$

- 4 : Output signal (HOUT) is triggered by the edge of input signal.

# **FUNCTIONAL DESCRIPTION**

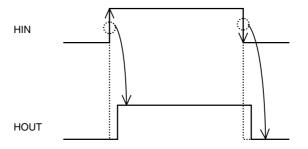

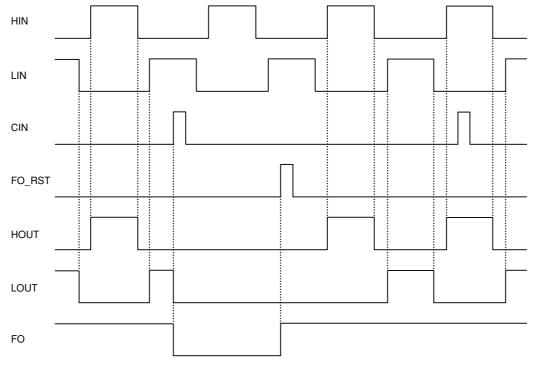

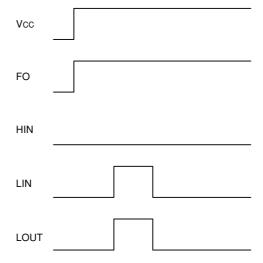

# 1. INPUT/OUTPUT TIMING DIAGRAM

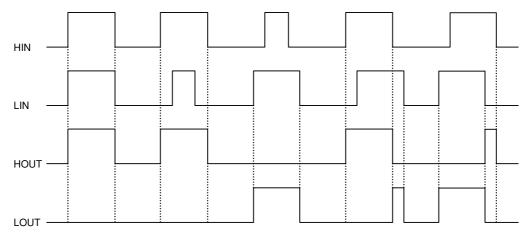

#### 2. INPUT INTERLOCK TIMING DIAGRAM

When the input signals (HIN/LIN) are high level at the same time, the outputs (HOUT/LOUT) keep their previous status. But if signals (HIN/LIN) are going to high level simultaneously, HIN signals will get active and cause HOUT to enter "H" status.

Note1: The minimum input pulse width at HIN/LIN should be to more than 500ns (because of HIN/LIN input noise filter circuit).

Note2: If a high-high status of input signals (HIN/LIN) is ended with only one input signal entering low level and another still being in high level, the output will enter high-low status after the delay match time (not shown in the figure above).

Note3: Delay times between input and output signals are not shown in the figure above.

#### 3. SHORT CIRCUIT PROTECTION TIMING DIAGRAM

When an over-current is detected by exceeding the threshold at the CIN and LIN is at high level at the same time, the short circuit protection will get active and shutdown the outputs while FO will issue a low level (indicating a fault signal). The fault output latch is reset by a high level signal at FO\_RST pin and then FO will return to high level while the output of the driver will respond to the following active input signal.

Note1: Delay times between input and output signals are not shown in the figure above.

Note2: The minimum FO\_RST pulse width should be more than 500ns (because of FO\_RST input filter circuit).

#### 1200V HIGH VOLTAGE HALF BRIDGE DRIVER

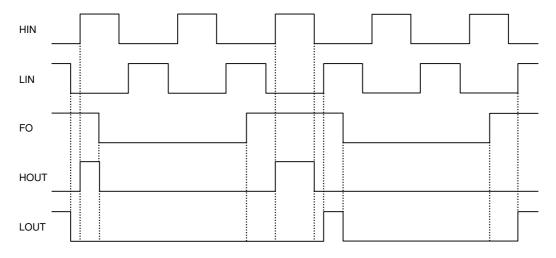

#### 4. FO INPUT TIMING DIAGRAM

When FO is pulled down to low level in case the FO of other phases becomes low level (fault happened) or the MCU/DSP sets FO to low level, the outputs (HOUT, LOUT) of the driver will be shut down. As soon as FO goes high again, the output will respond to the following active input signal.

Note1: Delay times between input and output signals are not shown in the figure above.

Note2: The minimum FO pulse width should be more than 500ns (because of FO input filter circuit).

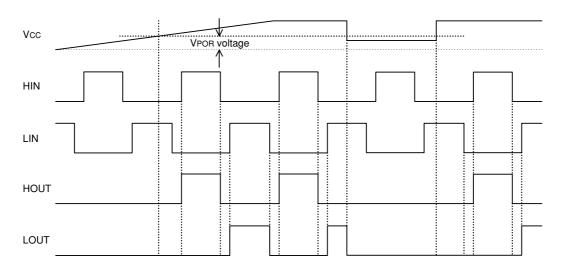

# 5. LOW SIDE Vcc SUPPLY POWER RESET SEQUENCE

When the Vcc supply voltage is lower than power reset trip voltage, the power reset gets active and the outputs (HOUT/LOUT) become "L". As soon as the Vcc supply voltage goes higher than the power reset trip voltage, the outputs will respond to the following active input signals.

$\label{thm:local_notation} \textbf{Note1: Delay times between input and output signals are not shown in the figure above.}$

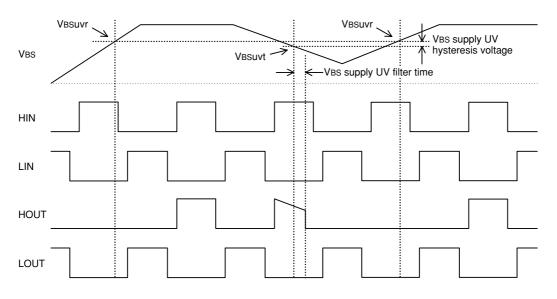

#### 6. HIGH SIDE VBS SUPPLY UNDER VOLTAGE LOCKOUT SEQUENCE

When VBs supply voltage drops below the VBs supply UV trip voltage and the duration in this status exceeds the VBs supply UV filter time, the output of the high side is locked. As soon as the VBs supply voltage rises above the VBs supply UV reset voltage, the output will respond to the following active HIN signal.

Note1: Delay times between input and output signals are not shown in the figure above.

# 7. POWER START-UP SEQUENCE

At power supply start-up the following sequence is recommended when bootstrap supply topology is used.

- (1). Apply Vcc.

- (2). Make sure that FO is at high level.

- (3). Set LIN to high level and HIN to low level so that bootstrap capacitor could be charged.

- (4). Set LIN to low level.

Note: If two power supply are used for supplying Vcc and VBs individually, it is recommended to set Vcc first and then set VBs.

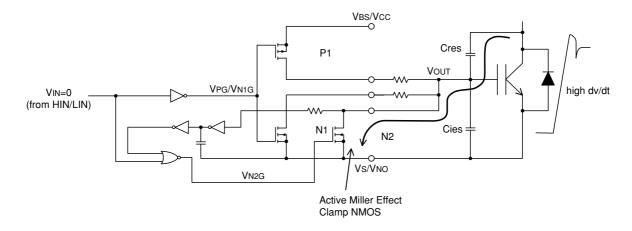

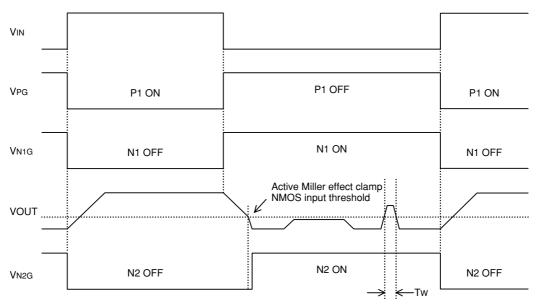

#### 8. ACTIVE MILLER EFFECT CLAMP NMOS OUTPUT TIMING DIAGRAM

The structure of the output driver stage is shown in following figure. This circuit structure employs a solution for the problem of the Miller current through Cres in IGBT switching applications. Instead of driving the IGBT gate to a negative voltage to increase the safety margin, this circuit structure uses a NMOS to establish a low impedance path to prevent the self-turn-on due to the parasitic Miller capacitor in power switches.

When HIN/LIN is at low level and the voltage of the VOUT (IGBT gate voltage) is below active Miller effect clamp NMOS input threshold voltage, the active Miller effect clamp NMOS is being turned on and opens a low resistive path for the Miller current through Cres.

Active Miller effect clamp NMOS keeps turn-on if Tw does not exceed active Miller clamp NMOS filter time

# 1200V HIGH VOLTAGE HALF BRIDGE DRIVER

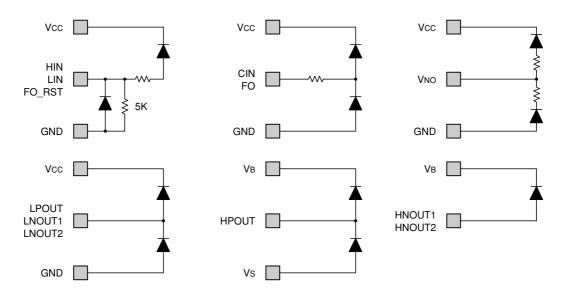

#### INTERNAL DIODE CLAMP CIRCUITS FOR INPUT AND OUTPUT PINS

# **PACKAGE OUTLINE**